EIROPAS SAVIENĪBA

#### IEGULDĪJUMS TAVĀ NĀKOTNĒ

ATTĪSTĪBAS FONDS

Latvijas Investīciju un attīstības aģentūra Investment and Development Agency of Latvia

#### **Concept of the reconfigurable communication** subsystem for custom modulation technique experiments with CubeSats

### Gatis Gaigals, Endija Briede, Roberts Trops, Jānis Šate

Presented research and development as part of the project No. L-KC-11-0006 are funded by **European Regional Development Fund**

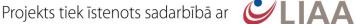

### **Experimental communication platform**

## RT-16 link budget advantage

#### Example:

- DQPSK 2.4 GHz

- 0.5W RF power

- Using simple "warm" receiver

- Data rate 5 Mbps

## **RF** section considerations

- SDR device

- Custom made RF frontend

- Solution from existing communication standards (Wi-Fi, Wi-Max)

- Relativly new technology Field Programmable Radio frequency (FPRF) chip

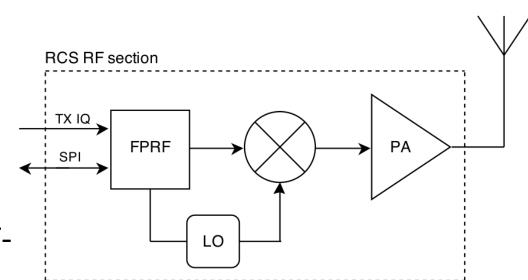

### Reconfigurable Communication Subsystem (RCS)

- C-band or S-band downlink

- Estimated data rate up to 10 Mbps

- RF output power 0.5 1 W

- Maximum power consumption ~10W

- Reconfigurable frequency, power, modulation, coding etc.

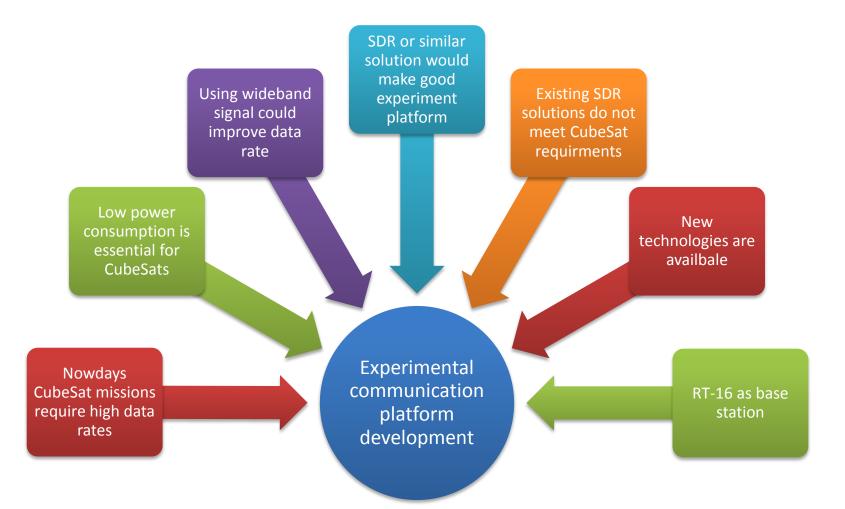

## **RCS** main sections

#### RF

- Data conversion

- Upconversion

- Amplification

#### FPGA

- High performance digital signal processing

- Memory

#### MCU

- Subsystem management

- Data interface

## RCS in conjuction with RT-16

- Requires frequency to be up-converted form 3.8 to 5.8 GHz

- Up-conversion significantly reduces power and PCB area budget

- S-band can be used (RT-16 would need a new receiver)

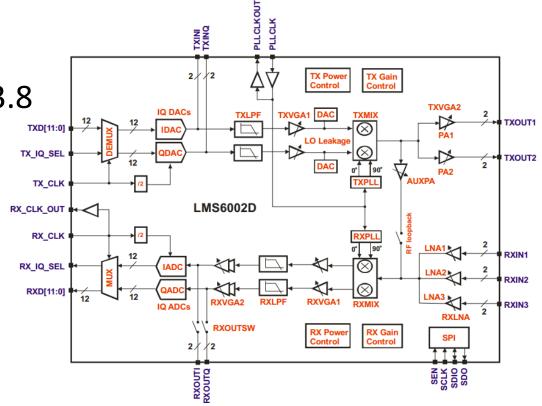

## FPRF

- Single chip transceiver

- Integrated ADCs/DACs

- Operating from 0.3 to 3.8 GHz

- Higly reconfigurable architecture

- Requires less PCB area and power

# MCU: programm memory

MCU is the hart of the system - reliability in free space flight

|                          | Flash  | EEPROM   | SRAM     | FRAM                     |  |

|--------------------------|--------|----------|----------|--------------------------|--|

| Non-volatile             | Yes    | Yes      | No       | Yes                      |  |

| Write endurance          | 10 000 | ~500 000 | Unlimite | 1 million billion        |  |

|                          |        |          | d        | (i.e. 10 <sup>15</sup> ) |  |

| Write speed (for 13 kB)  | 1s     | 2s       | <10ms    | 10ms                     |  |

| Average active power     | 260    | Up to 10 | <60      | 80                       |  |

| (µA/MHz)                 |        | mA       |          |                          |  |

| Dynamics bit addressable | No     | No       | Yes      | Yes                      |  |

| programmability          |        |          |          |                          |  |

## **MCU** selection

| Part Number   | GPIO | Package Group | Estimated Package Size (WxL)(mm <sup>2</sup> ) |  |

|---------------|------|---------------|------------------------------------------------|--|

|               |      |               | 40VQFN: 6 x 6: 36 mm2,                         |  |

| MSP430FR5849  | 33   | TSSOP, VQFN   | 38TSSOP: 6.2 x 12.5: 103 mm2                   |  |

|               |      |               | 40VQFN: 6 x 6: 36 mm2,                         |  |

| MSP430FR5859  | 33   | TSSOP, VQFN   | 38TSSOP: 6.2 x 12.5: 103 mm2                   |  |

| MSP430FR5869  | 40   | VQFN          | 48VQFN: 7 x 7: 49 mm2                          |  |

|               |      |               | 40VQFN: 6 x 6: 36 mm2,                         |  |

| MSP430FR5949  | 33   | TSSOP, VQFN   | 38TSSOP: 6.2 x 12.5: 103 mm2                   |  |

|               |      |               | 40VQFN: 6 x 6: 36 mm2,                         |  |

| MSP430FR5959  | 33   | TSSOP, VQFN   | 38TSSOP: 6.2 x 12.5: 103 mm2                   |  |

| MSP430FR5969  | 40   | VQFN          | 48VQFN: 7 x 7: 49 mm2                          |  |

| MSP430FR59691 | 40   | VQFN          | 48VQFN: 7 x 7: 49 mm2                          |  |

- FRAM non-volatile memory (64 KB FRAM and 2 KB SRAM)

- Ultra-low-power 16-bit MSP430 CPU

## **Command groups**

• FPRF- reconfiguration

General- RCS status and control

## Why FPGA?

Video

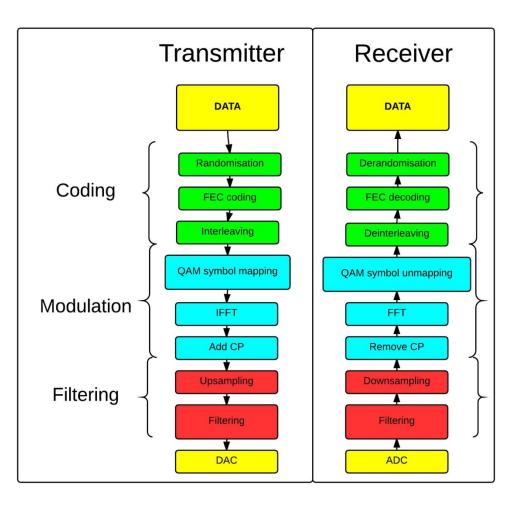

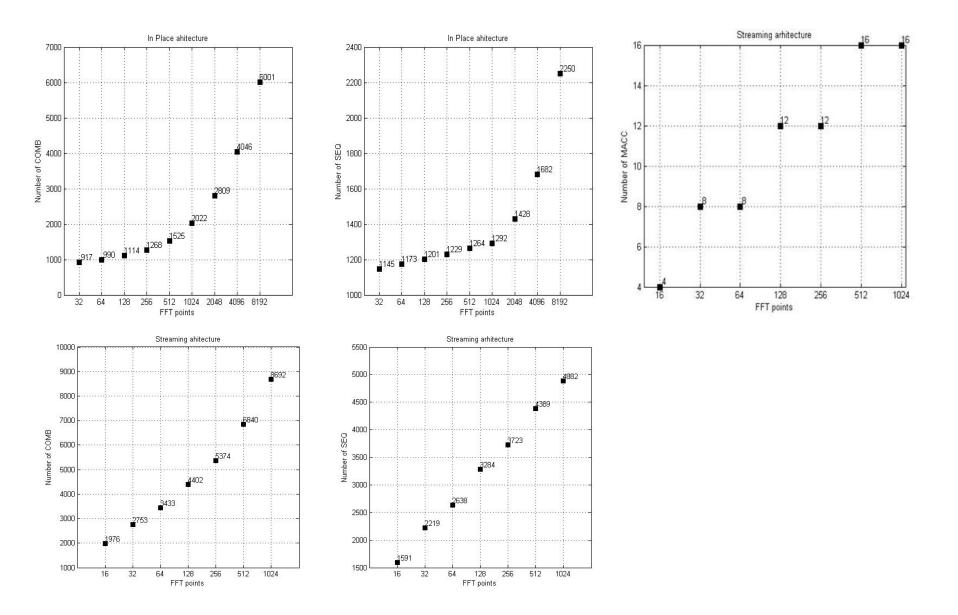

# FPGA based pipelined signal-path

Functionality:

- Coding/decoding

- Modulation/demodulation

- Upsampling/downsampling and filtering.

- All operations must be performed simultaneously in pipeline.

The bottleneck – high troughput IFFT/FFT core.

**Requirements:**

- Low power consumption

- High throughput FFT/IFFT core

- Sufficient amount of DSP blocks

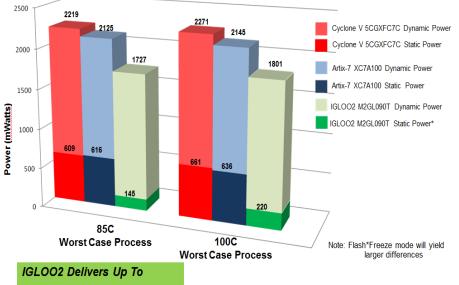

## Microsemi IGLOO2 Family

#### Advantages:

- Flash based FPGA technology

- Very low power consumption

- Flash\*Freeze mode

- <u>3X</u> Lower Static Power

- <u>25%</u>Lower Total Power

#### Overview of IGLOO2 family

|                                         | M2GL005 | M2GL010 | M2GL025 | M2GL050 | M2GL090 | M2GL100 | M2GL150 |

|-----------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Maximum Logic Elements<br>(4LUT + DFF)* | 6,060   | 12,084  | 27,696  | 56,340  | 86,316  | 99,512  | 146,124 |

| Math Blocks (18x18)                     | 11      | 22      | 34      | 72      | 84      | 160     | 240     |

| Total RAM (K bits)                      | 703     | 912     | 1104    | 1826    | 2586    | 3552    | 5000    |

## FPGA data storage

- Data buffer to ensure high data rate transmission;

- FPGA (M2GL010) memory resources:

- 256 kB Embedded Nonvolatile Memory;

- 64 kB Emebedded SRAM;

- 400 kb FPGA fabric memory;

- Trade-off between technology of external RAM:

- FRAM: less memory, lower power consumption;

- MRAM: more memory, higher power consumption during write cycle.

## Future work

- Transmitter > transceiver

- Up-converter design

- low power consumption

- low distortions

- Power amplifier design

- efficient to reduce power consumption

- linear enough

- FRAM/MRAM?

- new tech MCUs / FPGA based MCU?

- watch for a new generation FPRFs

# Conclusion

- Four main components board design is proposed:

- MCU: MSP430FR5869

- FPGA: Microsemi IGLOO2 M2GL010

- FPRF: LM6002D

- FRAM/MRAM

- Manufacturers provide information about their products in they own way

- Only downlink functionality will be implemented in initial design

- S-band will be used for initial design, upgrade to C in later versions (experiments with up-converter solutions)

- Development is on the way to make prototype

#### IEGULDĪJUMS TAVĀ NĀKOTNĒ

ATTĪSTĪBAS FONDS

Projekts tiek īstenots sadarbībā ar 😢 LIAA Latvijas Investīciju un attistības agentura Investment and Development Agency of Latvia

## Thank You!

Presented research and development as part of the project No. L-KC-11-0006 are funded by **European Regional Development Fund**